# Is Now Part of

# ON Semiconductor®

# To learn more about ON Semiconductor, please visit our website at www.onsemi.com

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="general-regarding-the-system-integration-to-fairchild-questions@onsemi.com">www.onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights or others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, s

# High-Current, Half-Bridge, Gate-Driver IC

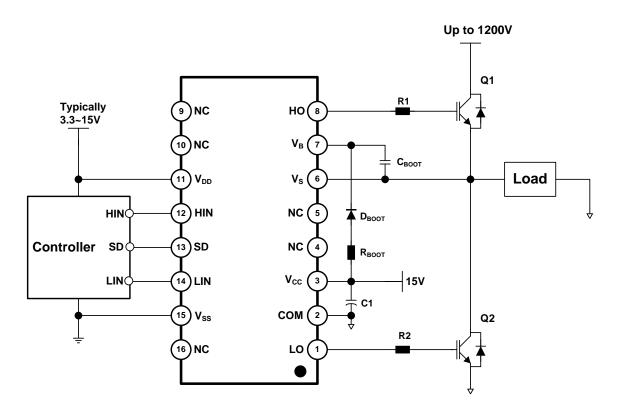

The FAN73912 is a monolithic half bridge gate-drive IC designed for high-voltage and high-speed driving for MOSFETs and IGBTs that operate up to  $\pm 1200~V$ .

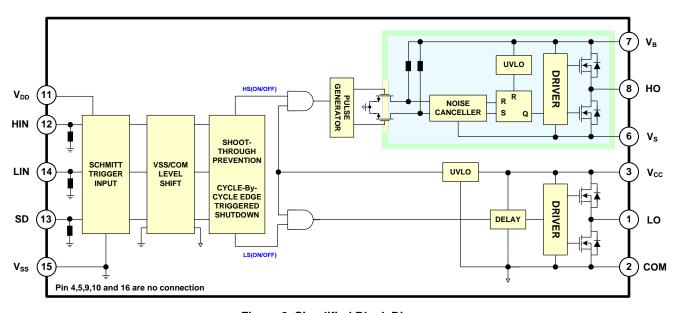

The advanced input filter of HIN provides protection against short-pulsed input signals caused by noise.

An advanced level-shift circuit offers high-side gate driver operation up to VS=-9.8 V (typical) for VBS=15 V. The UVLO circuit prevents malfunction when VCC and VBS are lower than the specified threshold voltage.

Output drivers typically source and sink 2 A and 3 A, respectively.

#### **Features**

- Floating Channel for Bootstrap Operation to +1200 V

- Typically 2 A/ 3 A Sourcing/Sinking Current Driving Capability for Both Channels

- Gate Driver Supply (VCC) Range from 12 V to 20 V

- Separate Logic Supply (VDD) Range from 3 V to 20 V

- Extended Allowable Negative VS Swing to -9.8 V for Signal Propagation at VCC=VBS=15 V

- Built-in Cycle-by-Cycle Edge-Triggered Shutdown Logic

- Built-in Shoot-Through Protection Logic

- Common-Mode dv/dt Noise Canceling Circuit

- UVLO Functions for Both Channels

- Built-in Advanced Input Filter

- Matched Propagation Delay Below 50 ns

- Outputs in-Phase with Input Signal

- Logic and Power Ground +/- 10 V Offset

#### **Typical Applications**

- Industrial Motor Driver

- UPS

- Solar Inverter

- Ballast

- General-Purpose Half-Bridge Topology.

# ON Semiconductor®

www.onsemi.com

#### **PACKAGE PICTURE**

Wide 16-SOIC

#### **MARKING DIAGRAM**

#### ORDERING INFORMATION

| Device                    | Package         | Packing<br>Method |

|---------------------------|-----------------|-------------------|

| FAN73912MX <sup>(1)</sup> | Wide16-<br>SOIC | Tape &<br>Reel    |

This device passed wave-soldering test by JESD22A-111

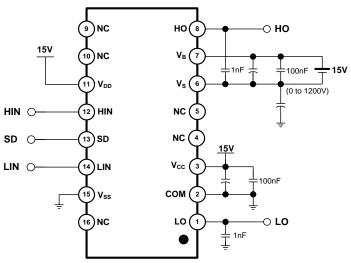

Figure 1. Application Schematic - Adjustable Option

Figure 2. Simplified Block Diagram

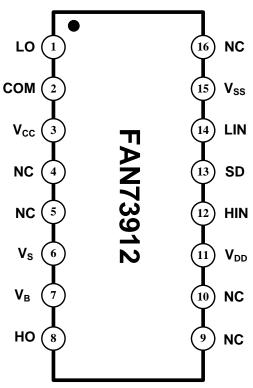

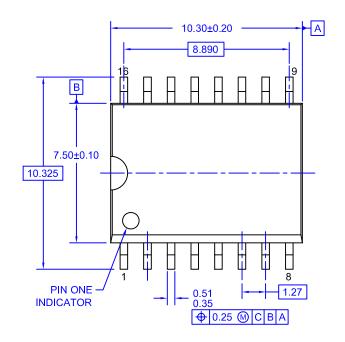

# **PIN CONNECTIONS**

Figure 3 Pin Connections – Wide 16-SOIC (Top View)

# PIN FUNCTION DESCRIPTION

| Pin No. | Pin Name        | Description                                  |

|---------|-----------------|----------------------------------------------|

| 1       | LO              | Low-Side Driver Output                       |

| 2       | COM             | Low-Side Driver return                       |

| 3       | VCC             | Low-Side Supply Voltage                      |

| 4       | NC              | No Connection                                |

| 5       | NC              | No Connection                                |

| 6       | V <sub>s</sub>  | High-Voltage Floating Supply Return          |

| 7       | V <sub>B</sub>  | High-Side Floating Supply                    |

| 8       | НО              | High-Side Driver Output                      |

| 9       | NC              | No Connection                                |

| 10      | NC              | No Connection                                |

| 11      | V <sub>DD</sub> | Logic Supply Voltage                         |

| 12      | HIN             | Logic Input for High-Side Gate Driver Output |

| 13      | SD              | Logic Input for Shutdown                     |

| 14      | LIN             | Logic Input for Low-Side Gate Driver Output  |

| 15      | V <sub>SS</sub> | Logic Ground                                 |

| 16      | NC              | No Connection                                |

#### MAXIMUM RATINGS (Note 2)

T<sub>A</sub>=25°C, unless otherwise specified. All voltage parameters are referenced to COM unless otherwise stated in the table.

| Symbol                        | Parameter                             | Min.                                    | Max.                 | Unit |

|-------------------------------|---------------------------------------|-----------------------------------------|----------------------|------|

| V <sub>B</sub>                | High-Side Floating Supply Voltage     | -0.3                                    | 1225.0               | V    |

| Vs                            | High-Side Floating Offset Voltage     | V <sub>B</sub> - 25                     | V <sub>B</sub> +0.3  | V    |

| V <sub>HO</sub>               | High-Side Floating Output Voltage     | V <sub>S</sub> -0.3                     | V <sub>B</sub> +0.3  | V    |

| V <sub>CC</sub>               | Low-Side Supply Voltage               | -0.3                                    | 25                   | V    |

| $V_{LO}$                      | Low-Side Floating Output Voltage      | -0.3                                    | V <sub>CC</sub> +0.3 | V    |

| $V_{DD}$                      | Logic Supply Voltage                  | V <sub>SS</sub> -0.3                    | V <sub>SS</sub> +25  | V    |

| V <sub>SS</sub>               | Logic GND                             | V <sub>DD</sub> -25                     | V <sub>DD</sub> +0.3 | V    |

| V <sub>IN</sub>               | Logic Input Voltage (HIN, LIN and SD) | V <sub>SS</sub> + V <sub>DD</sub> -25.3 | V <sub>DD</sub> +0.3 | V    |

| dV <sub>S</sub> /dt           | Allowable Offset Voltage Slew Rate    |                                         | ±50                  | V/ns |

| P <sub>D</sub> (Note 3, 4, 5) | Power Dissipation                     |                                         | 1.3                  | W    |

| $\theta_{JA}$                 | Thermal Resistance                    |                                         | 95                   | °C/W |

| TJ                            | Junction Temperature                  |                                         | 150                  | °C   |

| T <sub>STG</sub>              | Storage Temperature                   | -55                                     | 150                  | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. Mounted on 76.2 x 114.3 x 1.6 mm PCB (FR-4 glass epoxy material).

#### **RECOMMENDED OPERATING CONDITIONS**

All voltage parameters are referenced to COM.

| Symbol          | Parameter                                | Min.                                  | Max.                | Unit |

|-----------------|------------------------------------------|---------------------------------------|---------------------|------|

| V <sub>B</sub>  | High-Side Floating Supply Voltage        | V <sub>S</sub> +12                    | V <sub>S</sub> +20  | V    |

| Vs              | High-Side Floating Supply Offset Voltage | 8-V <sub>CC</sub>                     | 1200                | V    |

| $V_{HO}$        | High-Side (HO) Output Voltage            | Vs                                    | $V_B$               | V    |

| V <sub>CC</sub> | Low-Side Supply Voltage                  | 12                                    | 20                  | V    |

| $V_{LO}$        | Low-Side (LO) Output Voltage             | 0                                     | V <sub>CC</sub>     | V    |

| $V_{DD}$        | Logic Supply Voltage                     | V <sub>SS</sub> +3                    | V <sub>SS</sub> +20 | V    |

| V <sub>SS</sub> | Logic Ground (Note 6)                    | -10                                   | 10                  | V    |

| $V_{IN}$        | Logic Input Voltage (HIN, LIN, SD)       | V <sub>SS</sub> + V <sub>DD</sub> -20 | $V_{DD}$            | V    |

| T <sub>A</sub>  | Ambient Temperature                      | -40                                   | +125                | °C   |

When  $V_{DD}$ <10 V, the minimum  $V_{SS}$  offset is limited to - $V_{DD}$ .

<sup>3.</sup>

Refer to the following standards:

JESD51-2: Integral circuit's thermal test method environmental conditions, natural convection; JESD51-3: Low effective thermal conductivity test board for leaded surface-mount packages.

Do not exceed maximum power dissipation (P<sub>D</sub>) under any circumstances.

# STATIC ELECTRICAL CHARACTERISTICS

$V_{BIAS}(V_{CC}, V_{BS}, V_{DD})$  = 15.0 V,  $T_A$  = 25 °C, unless otherwise specified. The  $V_{IH}$ ,  $V_{IL}$  and  $I_{IN}$  parameters are referenced to  $V_{SS}$  and are applicable to respective input leads: HIN, LIN and SD. The  $V_O$  and  $I_O$  parameters are referenced to  $V_S$  and COM and are applicable to the respective output leads: HO and LO. The  $V_{DDUV}$  parameters are referenced to COM. The  $V_{BSUV}$  parameters are referenced to  $V_{S1,2,3}$ .

| Symbol              | Parameter                                                                      | Condition                                                       | Min. | Тур. | Max. | Unit |

|---------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------|------|------|------|------|

| OW-SIDE             | POWER SUPPLY SECTION                                                           |                                                                 | 1    | •    | •    |      |

| I <sub>QCC</sub>    | Quiescent V <sub>CC</sub> Supply Current                                       | V <sub>IN</sub> =0 V or V <sub>DD</sub>                         |      | 170  | 300  | μА   |

| $I_{QDD}$           | Quiescent V <sub>DD</sub> Supply Current                                       | V <sub>IN</sub> =0 V or V <sub>DD</sub>                         |      |      | 10   | μА   |

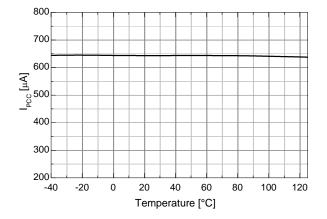

| I <sub>PCC</sub>    | Operating V <sub>CC</sub> Supply Current                                       | f <sub>IN</sub> =20 kHz, rms V <sub>IN</sub> =15V <sub>PP</sub> |      | 650  | 950  | μА   |

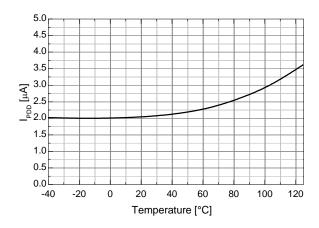

| I <sub>PDD</sub>    | Operating V <sub>DD</sub> Supply Current                                       | f <sub>IN</sub> =20 kHz, rms V <sub>IN</sub> =15V <sub>PP</sub> |      | 2    |      | μА   |

| I <sub>SD</sub>     | Shutdown Supply Current                                                        | S <sub>D</sub> =V <sub>DD</sub>                                 |      | 30   | 50   | μА   |

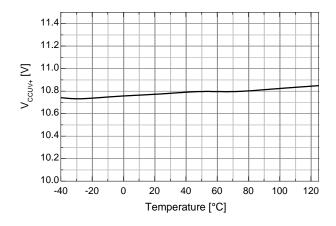

| V <sub>CCUV+</sub>  | V <sub>CC</sub> Supply Under-Voltage<br>Positive-Going Threshold Voltage       | V <sub>CC</sub> =Sweep                                          | 9.7  | 11.0 | 12   | V    |

| V <sub>CCUV</sub> - | V <sub>CC</sub> Supply Under-Voltage<br>Negative-Going Threshold Voltage       | V <sub>CC</sub> =Sweep                                          | 9.2  | 10.5 | 11.4 | V    |

| V <sub>CCUVH</sub>  | V <sub>CC</sub> Supply Under-Voltage Lockout<br>Hysteresis Voltage             | V <sub>CC</sub> =Sweep                                          |      | 0.5  |      | V    |

| BOOTSTR             | APPED SUPPLY SECTION                                                           |                                                                 |      | ul   | ul   |      |

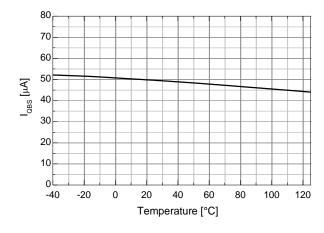

| I <sub>QBS</sub>    | Quiescent V <sub>BS</sub> Supply Current                                       | V <sub>IN</sub> =0 V or V <sub>DD</sub>                         |      | 50   | 100  | μА   |

| I <sub>PBS</sub>    | Operating V <sub>BS</sub> Supply Current                                       | f <sub>IN</sub> =20 kHz, rms value                              |      | 550  | 850  | μА   |

| V <sub>BSUV+</sub>  | V <sub>BS</sub> Supply Under-Voltage Positive-Going Threshold Voltage          | V <sub>BS</sub> =Sweep                                          | 9.7  | 11.0 | 12.0 | V    |

| $V_{BSUV}$          | V <sub>BS</sub> Supply Under-Voltage<br>Negative-Going Threshold Voltage       | V <sub>BS</sub> =Sweep                                          | 9.2  | 10.5 | 11.4 | V    |

| $V_{BSUVH}$         | V <sub>BS</sub> Supply Under-Voltage Lockout<br>Hysteresis Voltage             | V <sub>BS</sub> =Sweep                                          |      | 0.5  |      | V    |

| I <sub>LK</sub>     | Offset Supply Leakage Current                                                  | V <sub>B</sub> =V <sub>S</sub> =1200 V                          |      |      | 50   | μА   |

| NPUT Log            | jic SECTION(HIN.LIN and SD)                                                    |                                                                 |      | U    | u l  |      |

| V                   | Lasia IIdii Janua Valta sa                                                     | V <sub>DD</sub> =3 V                                            | 2.4  |      |      | V    |

| $V_{IH}$            | Logic "1" Input Voltage                                                        | V <sub>DD</sub> =15 V                                           | 9.5  |      |      | V    |

| W                   | Lasia IIOII Lasad Maliana                                                      | V <sub>DD</sub> =3 V                                            |      |      | 0.8  | V    |

| $V_{IL}$            | Logic "0" Input Voltage                                                        | V <sub>DD</sub> =15 V                                           |      |      | 6.0  | V    |

| I <sub>IN+</sub>    | Logic "1" Input bias Current                                                   | V <sub>IN</sub> =15 V                                           |      | 30   | 50   | μА   |

| I <sub>IN-</sub>    | Logic "0" Input bias Current                                                   | V <sub>IN</sub> =0 V                                            |      |      | 1    | μΑ   |

| R <sub>IN</sub>     | Logic Input Pull-down Resistance                                               |                                                                 |      | 500  |      | kΩ   |

| SATE DRI            | VER OUTPUT SECTION                                                             |                                                                 | •    |      |      |      |

| V <sub>OH</sub>     | High-Level Output Voltage, V <sub>BIAS</sub> -V <sub>O</sub>                   | I <sub>O</sub> =0 A                                             |      |      | 1.2  | V    |

| V <sub>OL</sub>     | Low-Level Output Voltage, Vo                                                   | I <sub>0</sub> =0 A                                             |      |      | 0.1  | V    |

| I <sub>O+</sub>     | Output HIGH Short-Circuit Pulse Current                                        | V <sub>O</sub> =0 V, V <sub>IN</sub> =5 V with PW≤10 μs         |      | 2.0  |      | Α    |

| I <sub>O</sub> .    | Output LOW Short-Circuit Pulsed Current                                        | V <sub>O</sub> =15 V, V <sub>IN</sub> =0 V with PW≤10 μs        |      | 3.0  |      | Α    |

| Vs                  | Allowable Negative V <sub>S</sub> Pin Voltage for HIN Signal Propagation to HO |                                                                 |      | -9.8 | -7.0 | V    |

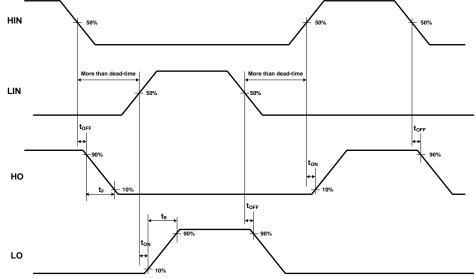

# **DYNAMIC ELECTRICAL CHARACTERISTICS**

$V_{BIAS}(V_{CC}, V_{BS}, V_{DD}) = 15.0 \text{ V}, V_S = V_{SS} = COM, C_L = 1000 \text{ pF} \text{ and } T_A = 25^{\circ}\text{C}, \text{ unless otherwise specified.}$

| Symbol             | Parameter                                    | Conditions              | Min. | Тур. | Max. | Unit |

|--------------------|----------------------------------------------|-------------------------|------|------|------|------|

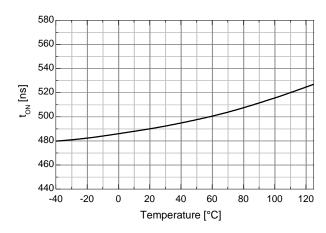

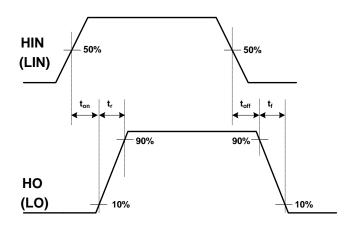

| t <sub>ON</sub>    | Turn-On Propagation Delay                    | V <sub>S</sub> =0 V     |      | 500  |      | ns   |

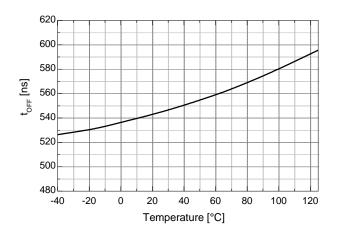

| t <sub>OFF</sub>   | Turn-Off Propagation Delay                   | V <sub>S</sub> =0V      |      | 550  |      | ns   |

| t <sub>FLTIN</sub> | Input Filtering Time (HIN, LIN) (Note7)      |                         | 80   | 150  | 220  | ns   |

| t <sub>FLTSD</sub> | Input Filtering Time (SD)                    |                         |      | 30   |      | ns   |

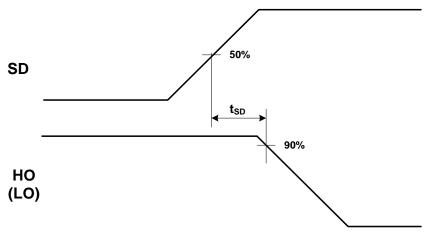

| t <sub>SD</sub>    | Shutdown Propagation Delay Time              |                         | 260  | 330  | 400  | ns   |

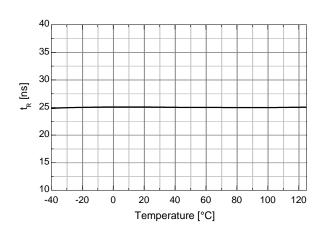

| t <sub>R</sub>     | Turn-On Rise Time                            |                         |      | 25   |      | ns   |

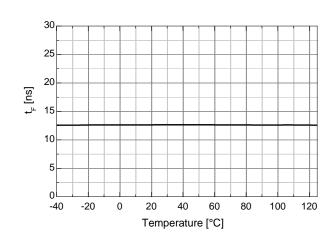

| t <sub>F</sub>     | Turn-Off Fall Time                           |                         |      | 15   |      | ns   |

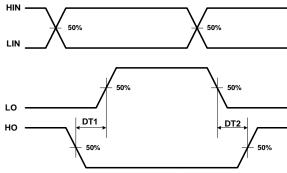

| DT                 | Dead Time                                    |                         | 200  | 330  | 450  | ns   |

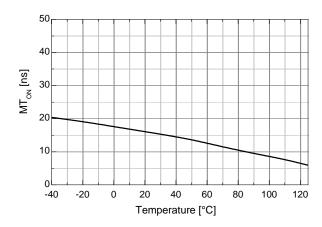

| MDT                | Dead-Time Matching (Note 8)                  |                         |      |      | 50   | ns   |

| MT                 | Delay Matching , HO & LO Turn-On/OFF(Note 9) |                         |      |      | 50   | ns   |

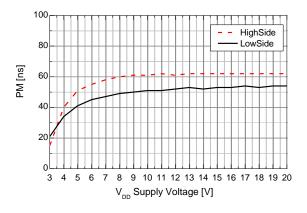

| PM                 | Output Pulse-Width Matching (Note 10)        | PW <sub>IN</sub> > 1 μs |      | 50   | 100  | ns   |

The minimum width of the input pulse should exceed 500 ns to ensure the filtering time of the input filter is exceeded.

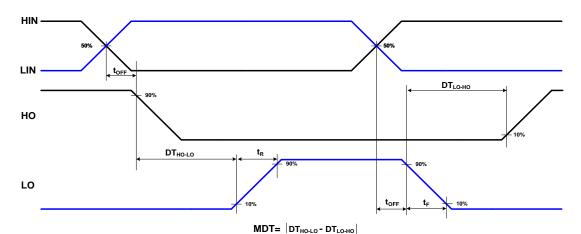

MDT is defined as | DT<sub>HO-LO</sub>-DT<sub>LO-HO</sub>| referenced to Figure 40.

MT is defined as an absolute value of matching delay time between High-side and Low-side

PM is defined as an absolute value of matching pulse-width between Input and Output.

Figure 4 Turn-On Propagation Delay vs. Temperature

Figure 5 Turn-Off Propagation Delay vs. Temperature

Figure 6 Turn-On Rise Time vs. Temperature

Figure 7 Turn-Off Fall Time vs. Temperature

Figure 8 Turn-On Delay Matching vs. Temperature

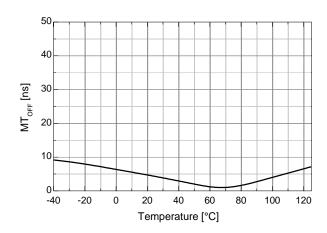

Figure 9 Turn-Off Delay Matching vs. Temperature

40 30 10 -40 -20 0 20 40 60 80 100 120 Temperature [°C]

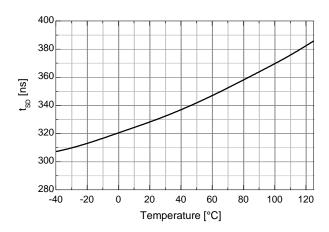

Figure 10 Shutdown Propagation Delay vs.

Temperature

Figure 11 Logic Input High Bias Current vs. Temperature

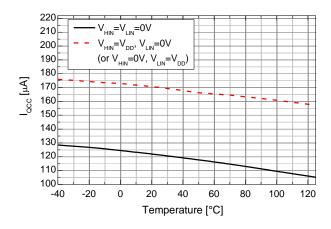

Figure 12 Quiescent V<sub>CC</sub> Supply Current vs. Temperature

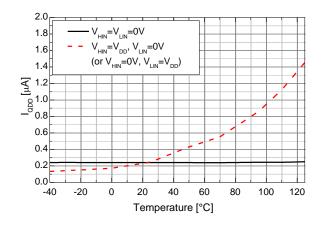

Figure 13 Quiescent V<sub>DD</sub> Supply Current vs. Temperature

Figure 14 Quiescent V<sub>BS</sub> Supply Current vs. Temperature

Figure 15 Operating V<sub>CC</sub> Supply Current vs. Temperature

Figure 16 Operating V<sub>DD</sub> Supply Current vs. Temperature

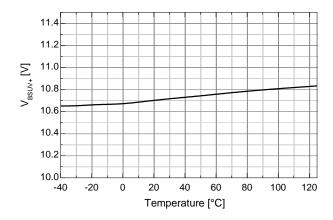

Figure 18 V<sub>CC</sub> UVLO+ vs. Temperature

Figure 20 V<sub>BS</sub> UVLO+ vs. Temperature

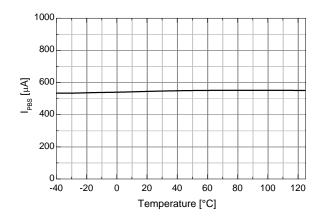

Figure 17 Operating V<sub>BS</sub> Supply Current vs. Temperature

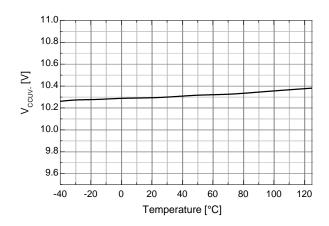

Figure 19 V<sub>CC</sub> UVLO- vs. Temperature

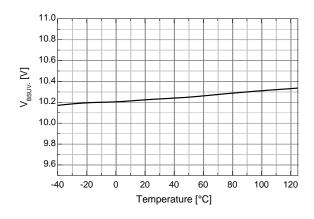

Figure 21 V<sub>BS</sub> UVLO- vs. Temperature

0.010 0.008 0.006 0.004 0.002  $\sim_{\rm ol} \mathbb{Z}$ 0.000 -0.002 -0.004 -0.006 -0.008 -0.010 -40 -20 0 20 40 60 100 120 Temperature [°C]

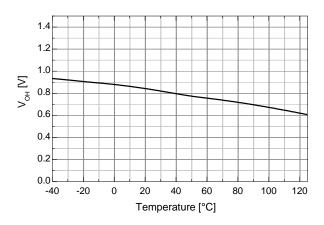

Figure 22 High-Level Output Voltage vs. Temperature

Figure 23 Low-Level Output Voltage vs. Temperature

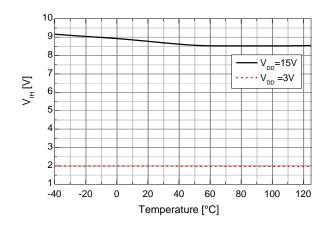

Figure 24 Logic High Input Voltage vs. Temperature

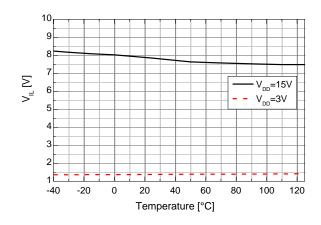

Figure 25 Logic Low Input Voltage vs. Temperature

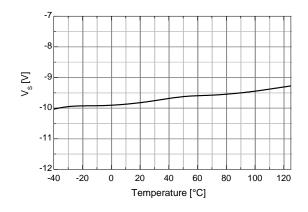

Figure 26 Allowable Negative V<sub>S</sub> vs. Temperature

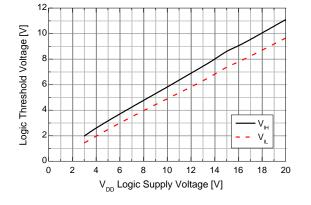

Figure 27 Input Logic(HIN&LIN) Threshold Voltage vs. V<sub>DD</sub> Supply Voltage

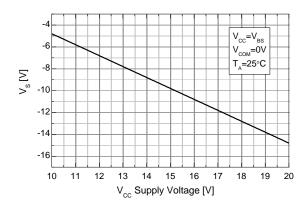

Figure 28 Allowable Negative Vs Voltage for HIN Signal Propagation to High Side vs.  $V_{CC}$  Supply Voltage

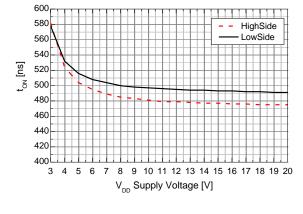

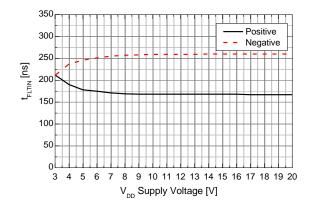

Figure 29 Turn-On Propagation Delay vs. V<sub>DD</sub> Supply Voltage

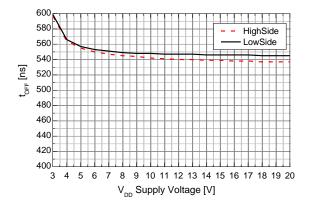

Figure 30 Turn-Off Propagation Delay vs. V<sub>DD</sub> Supply Voltage

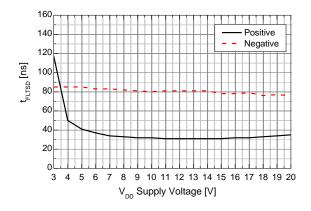

Figure 31 Logic Input Filtering Time vs. V<sub>DD</sub> Supply Voltage

Figure 32 Shutdown Input Filtering Time vs. V<sub>DD</sub> Supply Voltage

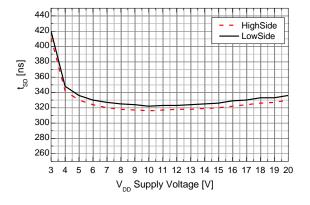

Figure 33 Shutdown Propagation Delay vs. V<sub>DD</sub> Supply Voltage

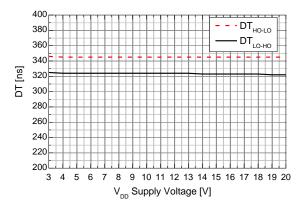

Figure 34 Dead Time vs. V<sub>DD</sub> Supply Voltage

Figure 36 Output Pulse-Width Matching vs. VDD Supply Voltage

Figure 35 Dead-Time Matching vs. V<sub>DD</sub> Supply Voltage

# **Switching Time Definitions**

Figure 37. Switching Time Test Circuit

Figure 38. Input/Output Timing Diagram

Figure 39. Switching Time Definition

# **Switching Time Definitions (continued)**

Figure 40. Internal Dead Time Definition

Figure 41. Switching Time Waveform Definitions

Figure 42. Switching Time Definitions

#### APPLICATIONS INFORMATION

#### **Dead Time**

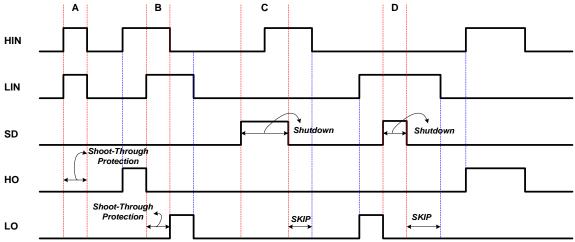

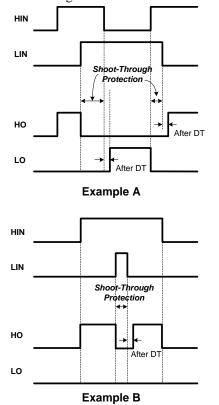

Dead time is automatically inserted whenever the dead time of the external two input signals (between HIN and LIN signals) is shorter than internal fixed dead times (DT1 and DT2). Otherwise, external dead times larger than internal dead times are not modified by the gate driver and internal dead-time waveform definition is shown in Figure 43.

Figure 43. Internal Dead-Time Definitions

#### **Protection Function**

#### **Shoot-Through Protection**

The shoot-through protection circuitry prevents both high- and low-side switches from conducting at the same time, as shown in Figure 44.

Figure 44. Shoot-Through Protection

#### **Shutdown Input**

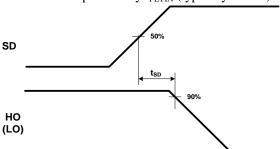

When the SD pin is in LOW state, the gate driver operates normally. When a condition occurs that should shut down the gate driver, the SD pin should be HIGH. The Shutdown circuitry has an input filter; the minimum input duration is specified by t<sub>FLTIN</sub> (typically 250 ns).

Figure 45. Output Shutdown Timing Waveform

# **Noise Filter**

#### **Input Noise Filter**

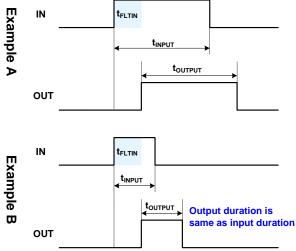

Figure 46 shows the input noise filter method, which has symmetry duration between the input signal ( $t_{INPUT}$ ) and the output signal ( $t_{OUTPUT}$ ) and helps to reject noise spikes and short pulses. This input filter is applied to the HIN, LIN, and EN inputs. The upper pair of waveforms (Example A) shows an input signal duration ( $t_{INPUT}$ ) much longer than input filter time ( $t_{FLTIN}$ ); it is approximately the same duration between the input signal time ( $t_{INPUT}$ ) and the output signal time ( $t_{OUTPUT}$ ). The lower pair of waveforms (Example B) shows an input signal time ( $t_{INPUT}$ ) slightly longer than input filter time ( $t_{FLTIN}$ ); it is approximately the same duration between input signal time ( $t_{INPUT}$ ) and the output signal time ( $t_{OUTPUT}$ ).

Figure 46. Input Noise Filter Definition

#### **Short-Pulsed Input Noise Rejection Method**

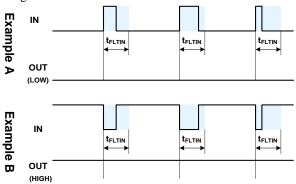

The input filter circuitry provides protection against short-pulsed input signals (HIN, LIN, and SD) on the input signal lines by applied noise signal.

If the input signal duration is less than input filter time  $(t_{\text{FLTIN}})$ , the output does not change states.

Example A and B of the Figure 47 show the input and output waveforms with short-pulsed noise spikes with a duration less than input filter time; the output does not change states.

Figure 47. Noise Rejecting Input Filter Definition

#### **Negative VS Transient**

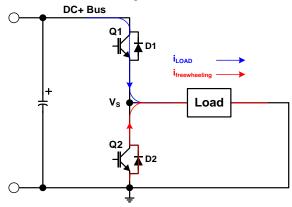

The bootstrap circuit has the advantage of being simple and low cost, but has some limitations. The biggest difficulty with this circuit is the negative voltage present at the emitter of the high-side switching device when high-side switch is turned-off in half-bridge application. If the high-side switch, Q1, turns-off while the load current is flowing to an inductive load, a current commutation occurs from high-side switch, Q1, to the diode, D2, in parallel with the low-side switch of the same inverter leg. Then the negative voltage present at the emitter of the high-side switching device, just before the freewheeling diode, D2, starts clamping, causes load current to suddenly flow to the low-side freewheeling diode, D2, as shown in Figure 48.

Figure 48. Half-Bridge Application Circuits

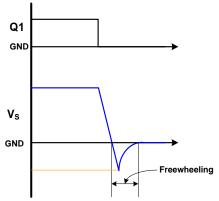

This negative voltage can be trouble for the gate driver's output stage, there is the possibility to develop an overvoltage condition of the bootstrap capacitor, input signal missing and latch-up problems because it directly affects

the source  $V_S$  pin of the gate driver, shown in Figure 49. This undershoot voltage is called "negative  $V_S$  transient".

Figure 49. V<sub>S</sub> Waveforms during Q1 Turn-Off

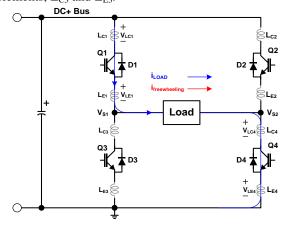

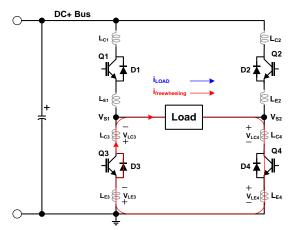

Figure 50 and Figure 51 show the commutation of the load current between high-side switch, Q1, and low-side freewheeling diode, D3, in same inverter leg. The parasitic inductances in the inverter circuit from the die wire bonding to the PCB tracks are jumped together in L<sub>C</sub> and L<sub>E</sub> for each IGBT. When the high-side switch, Q1, and low-side switch, Q4, are turned on, the  $V_{S1}$  node is below DC+ voltage by the voltage drops associated with the power switch and the parasitic inductances of the circuit due to load current is flows from O1 and O4, as shown in Figure 50. When the high-side switch, Q1, is turned off and Q4, remained turned on, the load current to flows the low-side freewheeling diode, D3, due to the inductive load connected to VS1 as shown in Figure 51. Q1 Turn-Off and D3 Conducting. The current flows from ground (which is connected to the COM pin of the gate driver) to the load and the negative voltage present at the emitter of the high-side switching device. In this case, the COM pin of the gate driver is at a higher potential than the  $V_S$  pin due to the voltage drops associated with freewheeling diode, D3, and parasitic elements, L<sub>C3</sub> and L<sub>E3</sub>.

Figure 50. Q1 and Q4 Turn-On

Figure 51. Q1 Turn-Off and D3 Conducting

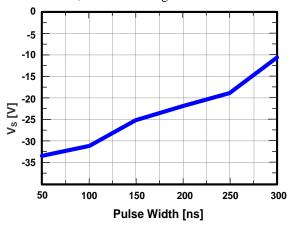

The FAN73912 has a typical negative V<sub>S</sub> transient characteristics, as shown in Figure 52.

Figure 52. Negative V<sub>S</sub> Transient Characteristic

Even though the FAN73912 has been shown able to handle these negative  $V_S$  transient conditions, it is strongly recommended that the circuit designer limit the negative  $V_S$  transient as much as possible by careful PCB layout to minimize the value of parasitic elements and component use. The amplitude of negative  $V_S$  voltage is proportional to the parasitic inductances and the turn-off speed, di/dt, of the switching device.

#### **General Guidelines**

## **Printed Circuit Board Layout**

The layout recommended for minimized parasitic elements is as follows:

- Direct tracks between switches with no loops or deviation.

- Avoid interconnect links. These can add significant inductance.

- Reduce the effect of lead-inductance by lowering package height above the PCB.

- Consider co-locating both power switches to reduce track length.

- To minimize noise coupling, the ground plane should not be placed under or near the high-voltage floating side.

- To reduce the EM coupling and improve the power switch turn-on/off performance, the gate drive loops must be reduced as much as possible.

# **Placement of Components**

The recommended placement and selection of component as follows:

- Place a bypass capacitor between the  $V_{CC}$  and  $V_{SS}$  pins. A ceramic 1  $\mu F$  capacitor is suitable for most applications. This component should be placed as close as possible to the pins to reduce parasitic elements.

- The bypass capacitor from V<sub>CC</sub> to V<sub>SS</sub> supports both the low-side driver and bootstrap capacitor recharge.

A value at least ten times higher than the bootstrap capacitor is recommended.

- The bootstrap resistor, R<sub>BOOT</sub>, must be considered in sizing the bootstrap resistance and the current developed during initial bootstrap charge. If the resistor is needed in series with the bootstrap diode, verify that V<sub>B</sub> does not fall below COM (ground). Recommended use is typically 5 ~ 10 Ω that increase the V<sub>BS</sub> time constant. If the voltage drop of bootstrap resistor and diode is too high or the circuit topology does not allow a sufficient charging time, a fast recovery or ultra-fast recovery diode can be used.

- The bootstrap capacitor, C<sub>BOOT</sub>, uses a low-ESR capacitor, such as ceramic capacitor. It is strongly recommended that the placement of components is as follows:

- Place components tied to the floating voltage pins (V<sub>B</sub> and V<sub>S</sub>) near the respective high-voltage portions of the device and the FAN73912. Not Connected (NC) pins in this package maximize the distance between the high-voltage and low-voltage pins (see Figure 3)

- Place and route for bypass capacitors and gate resistors as close as possible to gate drive IC.

- Locate the bootstrap diode, D<sub>BOOT</sub>, as close as possible to bootstrap capacitor, C<sub>BOOT</sub>.

- The bootstrap diode must use a lower forward voltage drop and minimal switching time as soon as possible for fast recovery or ultra-fast diode.

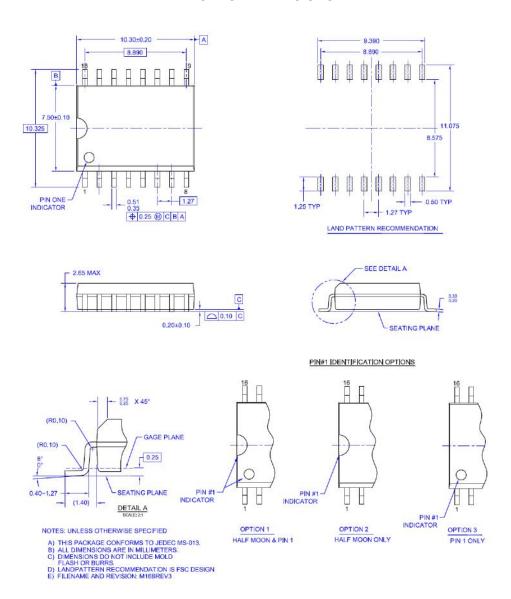

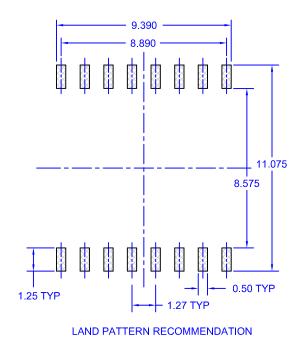

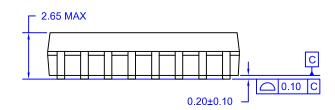

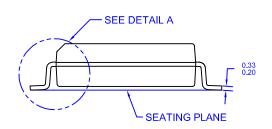

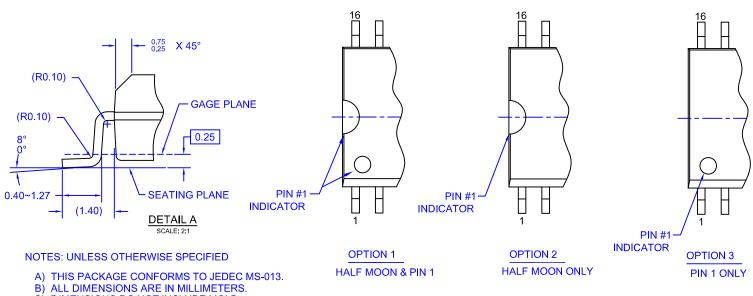

#### **PACKAGE DIMENSIONS**

Figure 53. 16-Lead, Small Outline Package(SOP)

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and requirements or standards. regardless of anv support or applications information ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA **Phone**: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada.

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

#### PIN#1 IDENTIFICATION OPTIONS

- DIMENSIONS DO NOT INCLUDE MOLD FLASH OR BURRS. C)

- D) LANDPATTERN RECOMMENDATION IS FSC DESIGN

- E) FILENAME AND REVISION: M16BREV3

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hol

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81–3–5817–1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative